# Conception des onduleurs de tension : Comparaison entre une structure classique et une structure multiniveau NPC

Culture Sciences de l'Ingénieur

LRevue 3E.I

Édité le 06/05/2024 école — — — normale — — supérieure — — paris — saclay — —

Adrien VOLDOIRE1

<sup>1</sup> Université Paris-Saclay, CentraleSupélec, CNRS, Laboratoire de Génie Electrique et Electronique de Paris (GeePs)

Cette ressource fait partie du N°112 de La Revue 3EI de mai 2024.

Cet article résume des considérations essentielles pour la conception des onduleurs de tension, qu'ils soient utilisés pour l'entrainement de machines triphasées ou pour la connexion à des réseaux de distribution ou embarqués. L'électrification massive des usages amenant un besoin d'efficacité énergétique accru, l'utilisation d'une structure d'onduleur classique 2 niveaux est comparée à une structure multiniveau dite Neutral Point Clamped (NPC). La comparaison devant reposer sur des indicateurs de rendement et de densité de puissance, des modèles analytiques sont proposés pour les deux structures. Ces modèles présentent des éléments clés pour le dimensionnement des transistors, diodes, inductances et condensateurs. Finalement, une analyse comparative sur trois dimensionnements permet de comprendre les enjeux sous-tendant le dimensionnement des onduleurs de tension et l'usage de structures multiniveaux.

## 1 - Introduction

Les onduleurs de tension sont indispensables pour réaliser de nombreuses fonctions centrales dans le cadre de l'électrification de usages et de la transition énergétique. On les retrouve par exemple dans l'intégration des énergies renouvelables sur le réseau, pour le pilotage des machines électriques synchrones et asynchrones, dans les alimentations sans interruption (ASI en français, UPS en anglais) des serveurs, ou encore dans la gestion de l'énergie électrique embarquée. L'électrification des usages amène à l'augmentation des puissances converties, en environnement souvent contraint, tout en améliorant les rendements énergétiques.

La réalisation de ces onduleurs devient alors critique, ce qui demande au concepteur d'innover en proposant des structures plus performantes et en choisissant rigoureusement les composants actifs et passifs. Ainsi, cet article propose une comparaison entre les performances d'un onduleur 2 niveaux, structure la plus classique, et celles d'un onduleur 3 niveaux Neutral Point Clamped (NPC), une des structures multiniveaux la plus mature dans l'industrie. Cette comparaison est réalisée à partir de modèles de pertes des composants actifs et passifs, dans le but d'évaluer correctement le rendement de chaque structure.

#### 2 - Structures d'onduleur 2 et 3 niveaux

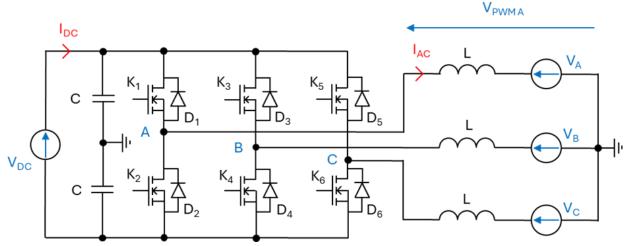

La Erreur! Source du renvoi introuvable. présente le schéma de l'onduleur de tension triphasé à 2 niveaux, intégrant 6 interrupteurs, 3 inductances de lissage et deux condensateurs de découplage. L'inductance de lissage n'est pas nécessaire dans le cas de l'entrainement d'une machine. Elle peut

être complétée par des condensateurs et d'autres inductances pour augmenter l'ordre du filtre dans le cas d'une connexion au réseau avec des contraintes de pollution harmonique sévère.

Figure 1 : Onduleur de tension triphasé avec filtrage

Les onduleurs multiniveaux sont apparus ces dernières décennies pour répondre aux cahiers des charges mettant en jeu des moyennes et fortes tensions. Le principe des structures multiniveaux [1] consiste à offrir plusieurs valeurs de tensions commutées, qui sont limitées à  $+V_{DC}$  et  $-V_{DC}$  dans le cas des onduleurs à 2 niveaux. Ainsi, une troisième valeur de tension, de valeur 0, est disponible en 3 niveaux. Cette valeur supplémentaire permet d'améliorer la qualité du signal côté alternatif, et donc de relâcher les contraintes sur le dimensionnement du filtre.

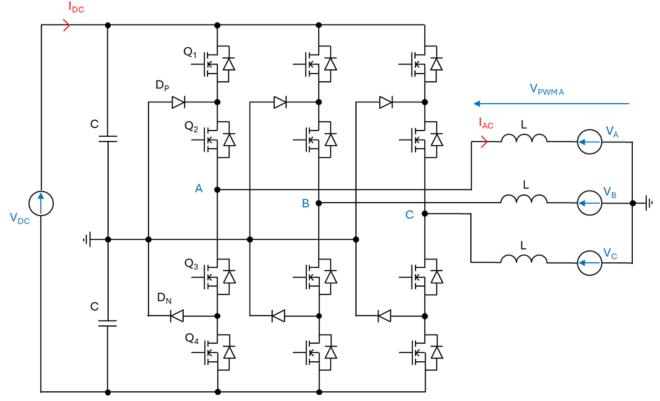

Un autre avantage des structures multiniveaux est de pouvoir répartir la tension du bus DC sur plusieurs interrupteurs au lieu d'un seul. Cela permet de choisir des interrupteurs de plus petit calibre en tension, ayant généralement de meilleures propriétés tout en étant plus facilement approvisionnables. Parmi les structures à 3 niveaux disponibles [2], [3], [4], la structure Neutral Point Clamped (NPC), représentée sur la **Erreur! Source du renvoi introuvable.**, est étudiée ici.

Figure 2: Structure Neutral Point Clamped 3 niveaux "NPC"

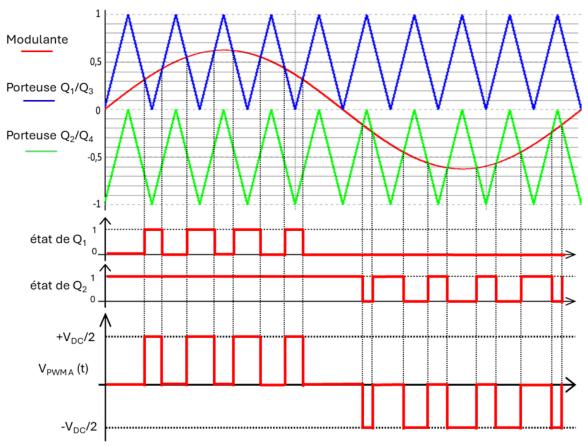

La structure NPC se commande naturellement en "Level Shift" ou "Phase Disposition", comme indiqué sur la Figure 3. La modulante est commune à tous les interrupteurs. La comparaison entre la modulante et la porteuse triangulaire en bleu contrôle les commutations complémentaires des interrupteurs  $Q_1$  et  $Q_3$ . La comparaison entre la modulante et la porteuse triangulaire en vert contrôle réciproquement  $Q_2$  et  $Q_4$ . L'analyse de l'état des interrupteurs, 1 signifiant passant et 0 bloqué, permet de tracer l'évolution de la tension simple, qui prend bien 3 valeurs :  $+V_{DC}/2$ , 0 et  $+V_{DC}/2$ .

Figure 3 : Illustration de la commande en Phase Disposition, de l'état des interrupteurs et de la tension simple d'un onduleur NPC

# 3 - Dimensionnement des interrupteurs de puissance

## 3.1 - Choix du calibre et de la technologie d'interrupteur

La réalisation d'un onduleur de tension impose le choix d'un interrupteur bidirectionnel en courant, unidirectionnel en tension. Pour réaliser cette fonction, une solution simple consiste à choisir un transistor MOSFET ou à associer un IGBT et une diode en antiparallèle. Bien qu'un transistor MOSFET possède déjà intrinsèquement une diode en antiparallèle, aussi appelée diode 'body', on ajoutera physiquement une diode, car la diode intrinsèque est de mauvaise qualité. L'hypothèse est faite que le transistor conduira les courants positifs, et la diode les courant négatifs.

Le choix d'un interrupteur se fait d'abord en regard des tensions mises en jeu. Le calibre en tension de l'interrupteur choisi doit être supérieur à la tension qu'il devra supporter, en raison des surtensions à chaque blocage. Le besoin critique de fiabilité dans de nombreux domaines, comme l'aéronautique ou l'automobile, amène à choisir un calibre en tension au moins égal à deux fois la tension à supporter.

$$V_{calibre} \ge 2V_{DC}$$

(1)

Pour une tension nominale de 540 V, le calibre en tension de l'interrupteur choisi est donc de 1200 V. Les transistors 1200 V disponibles sur le marché sont soit des IGBT en silicium, soit des MOSFET en carbure de silicium (SiC). Dans ce contexte, le choix d'interrupteur s'est porté sur les MOSFET SiC, qui ont comme propriétés remarquables des énergies de commutation bien plus faibles que pour les IGBT. Les diodes utilisées en antiparallèle seront des Schottky SiC, dont les pertes par recouvrement seront considérées négligeables devant les autres pertes.

Á la différence du choix du calibre en tension qui s'impose rapidement, le calibre en courant est bien plus difficile à choisir car il dépend de beaucoup de facteurs. Trois contraintes guident ce choix :

- <u>Le rendement</u> : les pertes issues des semi-conducteurs contribuent souvent majoritairement dans le calcul du rendement d'un convertisseur.

- <u>La température de jonction</u>: la température de jonction du transistor ne doit pas dépasser la température préconisée par le constructeur, souvent fixée entre 125°C et 150°C en fonction de la contrainte de fiabilité. Elle dépend de la quantité de pertes générée par les interrupteurs et du système de refroidissement mis en place pour évacuer ces pertes.

- <u>Le prix</u> : le prix est directement lié au calibre en courant d'un transistor et plus généralement à la surface de semiconducteur utilisée pour réaliser l'interrupteur.

Il apparait alors que le choix du calibre en courant résulte d'un compromis impliquant différentes variables d'entrée (dissipateur et fréquence de découpage), et plusieurs contraintes et performances critiques du convertisseur. La figure 4 montre deux technologies d'intégration de transistor : un composant discret pour les faibles courants et un module pour les forts courants. Par défaut, on peut choisir le calibre en courant à une valeur égale ou supérieure au courant efficace circulant dans le transistor.

Figure 4: MOSFET SiC du fabricant Cree: (a) packaging discret (TO247) et (b) packaging module

#### 3.2 - Pertes par conduction dans la structure 2 niveaux

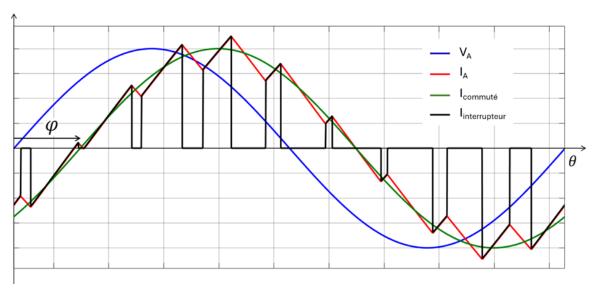

Les pertes par conduction existent car la résistance à l'état passant d'un interrupteur n'est jamais nulle. Pour évaluer les pertes en conduction, il est nécessaire de connaître le courant efficace et moyen dans les interrupteurs MOSFET et diode. Ces pertes sont calculées dans un seul interrupteur, elles sont identiques pour les 5 autres interrupteurs par symétrie des formes d'onde. La forme d'onde du courant dans un interrupteur (association d'un MOSFET et d'une diode) est donnée sur la **Erreur! Source du renvoi introuvable.**. La Figure 5 considère une fréquence de découpage très faible à des fins d'illustration pédagogique. Dans la réalité, on considère une fréquence de découpage au moins 100 fois plus grande que la fréquence fondamentale, ce qui permet un certain nombre d'hypothèses simplificatrices, dont le fait de négliger l'impact des ondulations de courant haute fréquence sur les pertes.

Figure 5 : Forme d'onde du courant dans un interrupteur pour un déphasage faible

Le temps de conduction d'un transistor dépend du rapport cyclique (2), variable au cours du temps en MLI bipolaire. La variable m définie par (3) représente l'indice de modulation en amplitude de l'onduleur, soit le rapport entre la valeur crête de la tension de sortie et la tension commutée, valant la moitié de la tension DC dans le cas de l'onduleur triphasé. Le courant commuté (4) est assimilé à un signal sinusoïdal parfait, avec  $\varphi$  le déphasage courant-tension en sortie d'onduleur entre les interrupteurs et le filtre.

$$\alpha(\theta) = \frac{1 + m.\sin(\theta)}{2} \tag{2}$$

$$m = \frac{2.V_{AC}\sqrt{2}}{V_{DC}} \tag{3}$$

$$I_{commut\acute{e}}(\theta) = I_{AC}\sqrt{2}\sin(\theta - \varphi)$$

(4)

Deux cas de figures sont ici possibles. Si l'interrupteur est composé uniquement d'un MOSFET, sans diode additionnel en anti-parallèle, l'expression du courant efficace dans le MOSFET est exprimée par (5) en fonction du courant commuté pondéré par le rapport cyclique  $\alpha(\theta)$ , et conduit à l'expression (6).

$$I_{T \ efficace} = \sqrt{\frac{1}{2\pi} \int_{0}^{2\pi} \alpha(\theta) I_{commut\acute{e}}(\theta)^{2} d\theta}$$

(5)

$$I_{Tefficace} = \frac{I_{AC}\sqrt{2}}{2} \tag{6}$$

Si on ajoute une diode en antiparallèle au transistor, on suppose alors que le courant positif passe par le MOSFET, et le courant négatif passe par la diode. Le transistor conduit alors sur une demipériode à la fréquence du réseau quand le courant commuté est positif, soit entre  $\varphi$  et  $\varphi + \pi$  (7). Une fois l'intégrale calculée, le courant efficace s'exprime analytiquement selon (8). Le même raisonnement est appliqué pour la diode complémentaire, en prenant en compte que son temps de conduction correspond à  $1 - \alpha(\theta)$ , ce qui conduit à (9) et (10).

$$I_{T \ efficace} = \sqrt{\frac{1}{2\pi} \int_{\varphi}^{\varphi + \pi} \alpha(\theta) I_{commut\acute{e}}(\theta)^2 d\theta}$$

(7)

$$I_{T\ efficace} = I_{AC}\sqrt{2}\sqrt{\frac{1}{8} + \frac{m}{3\pi}\cos(\varphi)}$$

(8)

$$I_{D \ efficace} = \sqrt{\frac{1}{2\pi} \int_{\varphi}^{\varphi + \pi} (1 - \alpha(\theta)) I_{commut\acute{e}}(\theta)^2 d\theta}$$

(9)

$$I_{D \ efficace} = I_{AC} \sqrt{2} \sqrt{\frac{1}{8} - \frac{m}{3\pi} \cos(\varphi)}$$

(10)

Le calcul des pertes dans une diode requiert également la connaissance du courant moyen, qui s'exprime selon (11) et (12).

$$I_{D \, moyen} = \frac{1}{2\pi} \int_{\varphi}^{\varphi + \pi} (1 - \alpha(\theta)) \, I_{commut\acute{e}}(\theta) d\theta \tag{11}$$

$$I_{D moyen} = \frac{I_{AC}\sqrt{2}}{2\pi} \left(1 - \frac{m.\pi}{4}\cos(\varphi)\right) \tag{12}$$

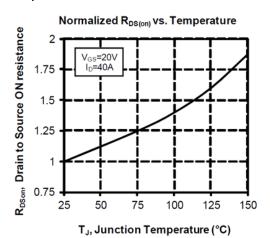

La résistance à l'état passant R<sub>DS on</sub> d'un transistor MOSFET SiC dépend fortement de la température de jonction de la puce, comme montré sur la **Erreur! Source du renvoi introuvable.**. La résistance est pratiquement multipliée par 2 en passant de 25°C à 150°C. Il convient alors de choisir la valeur de résistance pour le point de fonctionnement à puissance maximale, ce qui conduit généralement à une température de jonction supérieure à 100°C.

Figure 6 : Résistance normalisée à l'état passant d'un MOSFET en fonction de la température de jonction (données Microsemi)

Les pertes par conduction dans un transistor MOSFET dépendent uniquement de la résistance à l'état passant du transistor (13). A la différence des IGBT ou des diodes évoquées précédemment, il n'y a pas d'effet de seuil sur la tension. Les pertes en conduction dans une diode s'expriment selon (14), en prenant cette fois-ci en compte l'effet de tension de seuil  $V_{D0}$ .  $R_{D0}$  représente le coefficient directeur de la droite caractéristique de la diode dans le plan I-V.

$$P_{T\ conduction} = R_{DS\ on}.I_{T\ efficace}^{2} \tag{13}$$

$$P_{D \ conduction} = V_{D0}.I_{D \ moyen} + R_{D0}.I_{D \ efficace}^{2}$$

(14)

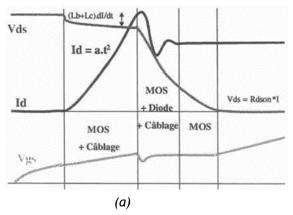

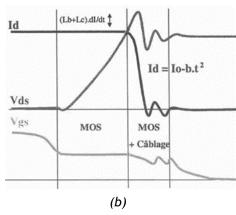

### 3.3 - Pertes par commutation dans la structure 2 niveaux

Chaque commutation, ouverture et fermeture, génère des pertes au sein des transistors. Cette énergie perdue s'explique par le fait que la tension aux bornes de l'interrupteur n'est pas nulle quand le courant s'établit et s'éteint dans le transistor. Les mécanismes de commutation, illustrés par la **Erreur! Source du renvoi introuvable.7**, sont expliqués en détail dans plusieurs travaux [5].

Figure 7: Mécanismes de commutation d'un MOSFET: (a) fermeture (ON) et (b) ouverture (OFF) [5]

Les énergies de commutation  $E_{on}$  et  $E_{off}$  dépendent notamment du courant et de la tension commutée. Dans le cas de l'onduleur de tension à 2 niveaux, la tension commutée est constante : c'est la tension  $V_{DC}$ . Comme les énergies de commutation sont caractérisées par le constructeur pour une tension d'essai  $V_{ref}$ , et qu'elles varient linéairement avec la tension, un coefficient linéaire est pris en compte.

En revanche, le courant commuté varie sinusoïdalement sur une période du réseau. Il est alors nécessaire de modéliser la variation des énergies de commutation en fonction du courant. Cette variation est donnée par le constructeur du module, elle est ici modélisée par une interpolation quadratique au moyen de coefficients  $a_T$ ,  $b_T$ , et  $c_T$ . L'expression indiquant la variation des énergies de commutation avec le courant et la tension est indiquée par (15).

$$(E_{on} + E_{off})(I, V) = \frac{V}{V_{ref}}(a_T I^2 + b_T I + c_T)$$

(15)

Les énergies de commutation dépendent également de l'environnement de commutation du transistor, qui peut accélérer ou ralentir la commutation. L'environnement de commutation regroupe la résistance de grille, les inductances parasites, le routage, la température, etc. Ces paramètres ne sont pas les mêmes entre l'essai réalisé par le constructeur pour construire la datasheet et le convertisseur réalisé. Il convient alors soit de caractériser ces énergies de commutation dans l'environnement de l'utilisateur, par exemple via un test en Double Pulse [6], soit d'admettre une imprécision réalisée dans l'estimation des pertes par commutation.

Les pertes en commutation dans un transistor se calculent sur une demi-période du réseau car les transistors ne commutent pas quand le courant est négatif. En effet, la diode anti-parallèle (intrinsèque ou ajoutée) conduisant pendant le temps mort précédant le blocage ou suivant l'amorçage, la tension aux bornes de l'interrupteur reste nulle pendant la commutation, ce qui annule les pertes.

Les pertes moyennes par commutation s'expriment alors selon (16). En considérant que le courant commuté est sinusoïdal (4), et en utilisant la variation quadratique de l'énergie en fonction du courant défini en (15), les pertes en commutation s'expriment analytiquement de la manière suivante (17).

$$P_{T\ commutation} = \frac{1}{2\pi} \int_{\varphi}^{\varphi + \pi} \left( E_{on}(\theta) + E_{off}(\theta) \right) f_{dec} \, d\theta \tag{16}$$

$$P_{T\ commutation} = \frac{V_{DC}}{V_{ref}} f_{dec} (\frac{a_T}{2} I_{AC}^2 + \frac{\sqrt{2} \cdot b_T}{\pi} I_{AC} + \frac{c_T}{2})$$

(17)

#### 3.4 - Pertes dans la structure NPC

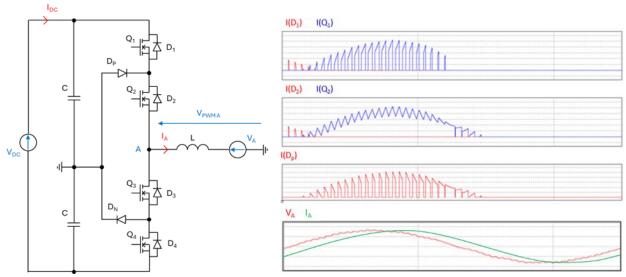

On appelle  $Q_1$  et  $Q_4$  les interrupteurs externes,  $Q_2$  et  $Q_3$  les interrupteurs internes,  $D_p$  et  $D_n$  les diodes de clamp. En analysant les formes d'onde présentées sur la **Erreur! Source du renvoi introuvable.8**, il apparait que l'interrupteur interne aura plus de pertes en conduction, alors que l'interrupteur externe aura plus de pertes en commutation.

Figure 8 : Formes d'onde en courant dans les interrupteurs d'un onduleur NPC

La méthode de calcul des pertes en conduction et en commutation s'inspire des méthodes développées précédemment. Les courants dans les diodes antiparallèles étant très faibles si le facteur de puissance de la charge est proche de 1, leurs expressions ne seront pas données par soucis de simplification. En configuration NPC, l'expression du rapport cyclique est différente de celle l'onduleur 2 niveaux (18).

$$\alpha(\theta) = m.\sin(\theta) \tag{18}$$

Les équations (19) et (20) indiquent le courant efficace dans un transistor externe ( $Q_1$  et  $Q_4$ ). Les équations (21) et (22) indiquent le courant efficace dans un transistor interne ( $Q_2$  et  $Q_3$ ).

Les équations (23), (24), (25) et (26) indiquent le courant dans une diode de clamp (Dp et Dn).

$$I_{RMS Q_1 NPC} = \sqrt{\frac{1}{2\pi} \int_{\varphi}^{\pi} \alpha(\theta) I_{commut\acute{e}}(\theta)^2 d\theta}$$

(19)

$$I_{RMS Q_1 NPC} = I_{AC} \sqrt{(1 + \cos(\varphi))^2 \frac{m}{3\pi}}$$

(20)

$$I_{RMS Q_2 NPC} = \sqrt{\frac{1}{2\pi} \left( \int_{\varphi}^{\pi} I_{commut\acute{e}}(\theta)^2 d\theta + \int_{0}^{\varphi} \left( 1 - \alpha(\theta) \right) I_{commut\acute{e}}(\theta)^2 d\theta \right)}$$

(21)

$$I_{RMS Q_2 NPC} = I_{AC} \sqrt{\left(\frac{1}{2} - (1 - \cos(\varphi))^2 \frac{m}{3\pi}\right)}$$

(22)

$$I_{RMS D_p NPC} = \sqrt{\frac{1}{2\pi} \int_{\varphi}^{\pi} (1 - \alpha(\theta)) I_{commut\acute{e}}(\theta)^2 d\theta} + \frac{1}{2\pi} \int_{\pi}^{\varphi + \pi} (1 + \alpha(\theta)) I_{commut\acute{e}}(\theta)^2 d\theta}$$

(23)

$$I_{RMS D_p NPC} = I_{AC} \sqrt{\left(\frac{1}{2} - \frac{2m}{3\pi} (1 + \cos(\varphi))^2\right)}$$

(24)

$$I_{moyen D_p NPC} = \frac{\frac{1}{2\pi} \int_{\varphi}^{\pi} (1 - \alpha(\theta)) I_{commut\acute{e}}(\theta) d\theta}{+ \frac{1}{2\pi} \int_{\pi}^{\varphi + \pi} (1 + \alpha(\theta)) I_{commut\acute{e}}(\theta) d\theta}$$

(25)

$$I_{moyen D_p NPC} = \frac{I_{AC}\sqrt{2}}{2\pi} \left(2 + m\left((\varphi - \frac{\pi}{2})\cos(\varphi) - \sin(\varphi)\right)\right)$$

(26)

Les pertes par commutation sont calculées pour un transistor externe  $(Q_1 \text{ et } Q_4)$  (27) (28), et pour un transistor interne  $(Q_2 \text{ et } Q_3)$  (29) (30), en considérant que la tension commutée est divisée par deux selon les avantages des structures 3 niveaux.

$$P_{Q1\ com} = \frac{V_{DC}}{2.V_{ref}} \frac{1}{2\pi} \int_{\omega}^{\pi} (E_{T\ on} + E_{T\ off}) . F_{dec} \, d\theta$$

(27)

$$P_{Q1\ com} = \frac{V_{DC}}{2.V_{ref}} \frac{f_{dec}}{2\pi} \cdot \begin{pmatrix} a_T \cdot I_{AC}^2 \left(\pi - \varphi + \frac{\sin(2\varphi)}{2}\right) \\ + b_T \cdot I_{AC}\sqrt{2} \cdot (1 + \cos(\varphi)) + c_T(\pi - \varphi) \end{pmatrix}$$

(28)

$$P_{Q2\ com} = \frac{V_{DC}}{2.V_{ref}} \frac{1}{2\pi} \int_{\pi}^{\pi+\varphi} (E_{T\ on} + + E_{T\ off}) F_{dec} \, d\theta \tag{29}$$

$$P_{Q2\ com} = \frac{V_{DC}}{2.V_{ref}} \frac{f_{dec}}{2\pi} \cdot \begin{pmatrix} a_T \cdot I_{AC}^2 \left( \varphi - \frac{\sin(2\varphi)}{2} \right) \\ + b_T \cdot I_{AC} \sqrt{2} \cdot (1 - \cos(\varphi)) + c_T \cdot \varphi \end{pmatrix}$$

(30)

#### 3.5 - Modèle thermique

Le fonctionnement des composants actifs de puissance, diode et transistor, génère des pertes qu'il convient d'évacuer. Classiquement, trois solutions sont envisagées : un refroidissement à eau, un refroidissement à air en convection forcée, ou un refroidissement à air en convection naturelle. La

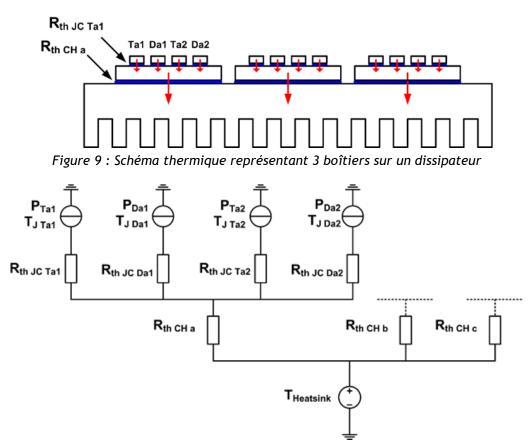

solution la plus performante est le refroidissement par eau, mais cela nécessite la mise en place d'un système hydraulique : pompe, échangeur thermique, régulations. La **Erreur! Source du renvoi introuvable.** 9 représente les flux de chaleur partant des interrupteurs jusqu'au dissipateur, ayant une température supposée fixe. Les pertes proviennent de trois boîtiers de puissance intégrant chacun deux transistors et deux diodes dans le cas de l'onduleur 2 niveaux. Le principe reste identique dans le cas du 3 niveaux, en ajoutant des boîtiers.

Classiquement, on considère que le flux de chaleur transportant les pertes de la puce au dissipateur est principalement freiné par deux résistances thermiques : la résistance thermique de contact 'junction to case' et la résistance thermique de contact 'case to heatsink'. La résistance 'junction to case' varie en fonction de la taille de l'interrupteur, la résistance 'case to heatsink' dépend de la qualité de la fixation du module sur le dissipateur et de sa surface. L'hypothèse est faite que la résistance thermique entre le boîtier et le dissipateur est unique, et pas distribuée pour chaque composant. Le schéma équivalent retenu est finalement proposé sur la **Erreur! Source du renvoi introuvable.10**.

Figure 10 : Réseau de résistance équivalent au schéma thermique

Les pertes dans chaque composant sont calculées comme indiqué précédemment. La valeur des résistances thermiques de contact peut être déduite à partir des données du constructeur. Selon le schéma thermique équivalent, les températures de jonction d'un MOSFET et d'une diode sont calculées selon (31) et (32). Les températures de jonction ne doivent par exemple pas dépasser 125°C pour assurer une bonne fiabilité.

$$T_{J MOSFET} = T_{sink} + P_{MOSFET}R_{th JC MOSFET} + (2P_{MOSFET} + 2P_{diode})R_{th CH}$$

(31)

$$T_{J \, diode} = T_{sink} + P_{diode}R_{th \, JC \, diode} + (2P_{MOSFET} + 2P_{diode})R_{th \, CH}$$

(32)

# 4 - Dimensionnement des composants passifs

## 4.1 - Dimensionnement des inductances de lissage

Le dimensionnement des inductances de lissage en sortie d'onduleur répond au besoin de filtrage des harmoniques issues du découpage dans le cas de la connexion réseau. De nombreuses contraintes régissent le dimensionnement de ces inductances :

- Garantir une valeur d'inductance suffisante pour la contrainte de Taux de Distorsion Harmonique (THD) du réseau imposé par des normes (EN/CEI 61000-3-2). Cette contrainte n'est pas discutée ici car elle dépend de l'ordre de filtre sélectionné (L, LC, LCL, etc...). Cela nécessite le développement de modèles fréquentiels ou le couplage à une simulation circuit.

- Garantir une valeur d'inductance faible pour ne pas absorber trop de puissance réactive. Une contrainte empirique simple consiste à limiter la chute de tension aux bornes du composant à 10% du fondamental du réseau.

- Garantir une induction crête dans le noyau inférieur à l'induction à saturation du matériau magnétique. Le calcul d'induction est présenté dans les lignes qui suivent.

- Garantit la capacité de bobiner le nombre de spires requis dans la fenêtre de bobinage.

- Garantir une température de composant raisonnable pour ne pas dégrader ses propriétés. Á

défaut de modèles thermiques viables quel que soit la géométrie, on prendra comme image

de cette contrainte la densité de courant dans le bobinage et les pertes volumiques dans le

noyau.

- Garantir des pertes, une masse, un volume ou un prix minimal en fonction du cahier des charges de l'utilisateur.

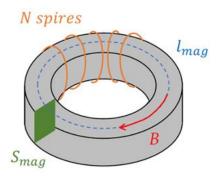

La méthode présentée ici consiste à calculer en premier lieu la variation de tension aux bornes de l'inductance, qui ne dépend pas de la valeur de cette dernière. Les expressions développées ciaprès ne sont valables que dans le cas où les références de potentiel DC et AC sont communes, comme indiqué sur la figure 1. Dans ce cas de figure, à l'échelle d'une période haute fréquence, l'ondulation de tension (32) est calculée entre 0 et  $\alpha T$ , avec  $V_{PWM}$  valant  $V_{DC}/2$  sur cet intervalle, et  $\omega_{grid} = 2\pi f_{grid}$ . Connaissant cette grandeur, il est possible de calculer la variation d'induction grâce à la loi de Lenz-Faraday énoncée selon (33). Cette écriture suppose que l'induction est uniforme dans le noyau de section  $S_{mag}$  autour duquel sont bobinées  $N_{spires}$  spires. Ces paramètres sont représentés sur la Figure 11, en considérant une inductance à noyau torique.

$$\Delta V(t) = \frac{V_{DC}}{2} - V_{AC}\sqrt{2}\sin(\omega_{grid}.t)$$

(32)

$$\Delta B(t) = \frac{1}{N_{spires}S_{mag}} \int_{0}^{\alpha T} \Delta V dt$$

(33)

Figure 11 : Définition des paramètres de l'inductance torique

En supposant que l'ondulation de tension  $\Delta V$  ne dépend pas de la variation de tension du réseau  $V_{AC}$  à l'échelle de l'intégration sur une période de découpage, et en considérant l'expression du coefficient de réglage m, l'ondulation d'induction est formulée en (34).

$$\Delta B(t) = \frac{V_{DC}(1 - m^2.(\sin(\omega_{grid}.t))^2)}{4N_{spires}S_{mag}f_{dec}}$$

(34)

Cette valeur d'ondulation permet le calcul des pertes volumiques fer dans le noyau. L'équation (35) utilise le modèle de Steinmetz [7], en réduisant l'ondulation à un sinus d'amplitude  $\frac{\Delta B(0)}{2}$ , ce qui représente la valeur maximale d'ondulation, à la fréquence de découpage  $F_{dec}$ . Les coefficients k, a et b se déduisent des abaques fournies par le fabricant du matériaux magnétique [8]. La valeur des pertes volumiques dans le noyau doit être maitrisée, car la température du noyau augmente environ de 10°C par tranche 100 mW par cm³ de pertes fer en convection naturelle.

$$P_{vol\,noyau} = k. f_{dec}^{\ a} \cdot \frac{\Delta B(0)^b}{2}$$

(35)

L'évaluation de l'induction crête (36) est nécessaire pour vérifier qu'on ne dépasse pas l'induction à saturation du noyau. On utilise ici l'hypothèse d'un matériau ayant une perméabilité relative constante  $\mu_r$ , matériau en régime linéaire non saturé, et un champ parcourant un contour de longueur  $l_{mag}$ , sans entrefer.

$$B_{crête} = \frac{N_{spires}.\,\mu_r.\,\mu_0}{l_{mag}} I_{L\,AC} \sqrt{2}$$

(36)

Les contraintes sur le noyau ayant été énoncées, il reste à écrire celles pour les conducteurs. Une première contrainte de nature géométrique consiste à s'assurer que l'intégralité des  $N_{spires}$  spires rentre dans la fenêtre de bobinage du noyau. La surface de bobinage ne doit pas être remplie à plus de 50% pour assurer le passage d'une navette lors du bobinage des spires. Il est également possible d'imposer un bobinage monocouche pour éviter les effets capacitifs entre les spires de différentes couches, ce qui génèrerait davantage de perturbations électromagnétiques.

Enfin, l'évaluation du courant est indispensable pour choisir la section de cuivre, calculer les pertes dans le conducteur, et éviter un échauffement trop important.

L'ondulation de courant se déduit directement de l'ondulation d'induction. La formulation (37) fait apparaître la valeur d'inductance L.

$$\Delta I_{LAC}(t) = \frac{l_{mag}.\Delta B(t)}{N_{spires}.\mu_{r}.\mu_{0}} = \frac{V_{DC}(1 - m^{2}.(\sin(\omega_{grid}.t))^{2})}{4.L.f_{dec}}$$

(37)

Les pertes cuivre résultent du toutes les composantes harmoniques du courant circulant dans l'inductance. En considérant que l'ondulation de courant est de forme triangulaire, en prenant sa valeur maximale à t = 0. Les pertes cuivre s'expriment selon (38).

$$P_{cuivre} = R(f_{grid}) \cdot I_{LAC}^{2} + R(f_{dec}) \cdot (\frac{\Delta I_{LAC}(0)}{2\sqrt{2}})^{2}$$

(38)

La résistance du bobinage à la fréquence fondamentale du réseau est très proche de la résistance DC, mais ce n'est pas forcément le cas à la fréquence de découpage. Dans les conducteurs massifs, les électriciens ont remarqué depuis longtemps que le courant alternatif préfère circuler à la périphérie du conducteur. Cela s'explique par la formation de courants induits par le champ magnétique généré par le courant alternatif haute fréquence. Ces courants induits s'additionnent au courant alternatif à la périphérie du conducteur, alors qu'ils s'annulent au centre : il s'agit de l'effet de peau. Boucherot définit l'épaisseur de peau  $\delta$  (39) comme une constante définissant la largeur approximative de la zone où se concentre le courant dans un conducteur en fonction de la fréquence du signal.

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}} \tag{39}$$

avec  $\mu$  la perméabilité magnétique du conducteur,  $\rho$  la résistivité du conducteur et f la fréquence du signal.

La formule de Levasseur [9] donne une bonne approximation de la résistance d'un conducteur en fonction de la fréquence. La formule (40) donne le rapport entre la résistance DC et la résistance à la fréquence f, pour un conducteur de rayon r.

$$\frac{R_{AC}}{R_{DC}}(f) = \frac{1}{4} + \sqrt[6]{0.178 + (\frac{r}{2\delta})^6}$$

(40)

Pour finir, la section du conducteur doit être suffisante pour éviter un échauffement excessif. Une bonne pratique consiste à adopter une densité de courant inférieure à 5 A/mm², cette valeur pouvant être modulée par la quantité de pertes par effet de peau et par la technologie de refroidissement mise en œuvre.

Les modèles développés ici dans le cas de l'onduleur 2 niveaux, peuvent être extrapolés au cas de l'onduleur NPC en considérant l'expression du rapport cyclique (18).

#### 4.2 - Dimensionnement des condensateurs de découplage du bus DC

Les condensateurs du bus DC permettent un filtrage efficace des harmoniques générées par les onduleurs MLI pour tenir les contraintes de qualité d'énergie du signal absorbé par le convertisseur. Le volume de ces condensateurs représente souvent une part non négligeable des onduleurs. Le dimensionnement des condensateurs dépend principalement du calibre en tension (imposé par l'application), de la valeur de capacité (nécessaire pour la fonction de filtrage), mais aussi du courant efficace traversant le composant. Très souvent, ce dernier paramètre est contraignant dans le dimensionnement du condensateur. Une approximation du courant efficace dans le condensateur est indiqué en (41) [10].

$$I_{Cefficace} = \frac{I_{AC}\sqrt{2}}{2} \tag{41}$$

Une particularité de la structures NPC réside dans la présence d'une harmonique basse fréquence dans le spectre du courant dans les condensateurs d'entrée. Cette harmonique basse fréquence circule par les diodes de clamp jusqu'au point milieu capacitif, pour ensuite repartir dans le convertisseur, sans jamais atteindre la source [11]. Il s'agit en quelque sorte d'un courant de mode commun. L'harmonique qui ressort principalement est à trois fois la fréquence du réseau, elle peut s'approximer selon (42).

$$I_{C \, NPC \, h3} = \frac{4m}{5\pi} I_{AC} \tag{42}$$

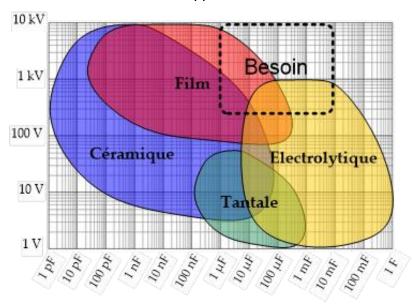

Il existe une multitude de technologies de condensateur adaptées à la conception des convertisseurs de puissance. La tension du condensateur affichée par le constructeur doit être supérieure à celle que le composant doit tenir pour des raisons de fiabilité. Les plus communes d'entre elles sont représentées sur la **Erreur! Source du renvoi introuvable.2**, en fonction de la valeur de capacité voulue et de la tension à supporter.

Figure 12 : Choix de la technologie de condensateur en fonction de la tension et de la capacité

En considérant les niveaux de tensions et de courant du cahier des charges, deux technologies de condensateurs se distinguent : les condensateurs film et les condensateurs électrolytiques. Les condensateurs films admettent un courant efficace élevé, mais l'énergie volumique stockable est assez faible, ce qui conduit à un gros volume de composant à iso-tension et iso-capacité par rapport à d'autres technologies. Á l'inverse, les condensateurs aluminium électrolytique ont une moins bonne tenue en courant, vieillissent plus rapidement, mais ils sont plus légers que les condensateurs films.

# 5 - Comparaison des structures

On souhaite ici étudier la pertinence de la montée en tension dans le domaine aéronautique. En effet, l'électrification des fonctions propulsives et non-propulsives des actionneurs embarqués dans les aéronefs représente une solution prometteuse pour diminuer l'impact environnemental de cette filière [12]. Dans le contexte de l'augmentation des puissances embarquées, la montée en tension et le recours à des architectures multiniveaux est une solution pour diminuer les pertes des systèmes électriques. Le Tableau 1 reprend donc un cahier des charges avec des tensions aéronautiques actuellement utilisées dans le Boeing 787 (540 Vdc et 115 Vac), et envisage l'augmentation de ces valeurs pour répondre au besoin d'un actionneur de forte puissance (90 kW).

| Cahier des charges                |            |       |            |

|-----------------------------------|------------|-------|------------|

| Description                       | Variable   | Unité | Valeur     |

| Puissance active de la charge     | Р          | W     | 90 000     |

| Facteur de puissance de la charge | PF         | -     | 0.9        |

| Fréquence réseau                  | $f_{grid}$ | Hz    | 400        |

| Fréquence de découpage            | $f_{dec}$  | Hz    | Variable   |

| Tension du bus DC                 | $V_{DC}$   | ٧     | 540 ou 900 |

| Tension AC efficace phase-neutre  | $V_{AC}$   | ٧     | 115 ou 230 |

Tableau 1 : Cahier des charges utilisé pour la comparaison

Les modèles développés plus haut sont intégrés dans un outil de dimensionnement permettant une comparaison des performances. La méthodologie de conception n'est pas développée ici. Un algorithme d'optimisation [13] vient proposer différentes solutions pour les deux cahiers des charges, en présentant les résultats sous forme de front de Pareto avec deux variables : la masse du convertisseur et son rendement. Des modèles de masse de composant sont donc intégrés dans l'outil, avec entre autres la masse d'échangeur thermique nécessaire au refroidissement du convertisseur estimée à 1.5 kg par kW de pertes.

Le cas de référence consiste à utiliser un onduleur 2 niveaux avec les tensions actuelles. Le second cas se résume à élever les tensions mises en jeu. Le troisième cas consiste à remplacer la structure 2 niveaux par une structure NPC dans le cas des tensions plus élevées. L'analyse des signaux commutés amène à changer le calibre en tension et en courant des interrupteurs dans chaque cas :

- Onduleur 2 niveaux avec  $V_{dc}$  = 540 V  $\rightarrow$  calibre de 1200 V

- Onduleur 2 niveaux avec  $V_{dc}$  = 900 V  $\rightarrow$  calibre de 1700 V

- Onduleur NPC avec V<sub>dc</sub> = 900 V → calibre de 900 V

La gamme de MOSFET en carbure de silicium (SiC) du fabricant Microchip est utilisée. Le choix du calibre en courant des interrupteurs, la fréquence de découpage ainsi que le dimensionnement des composants passifs sont optimisés par l'algorithme.

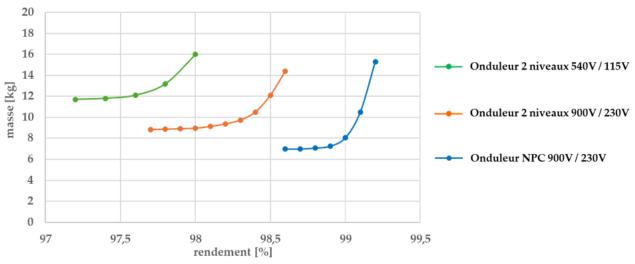

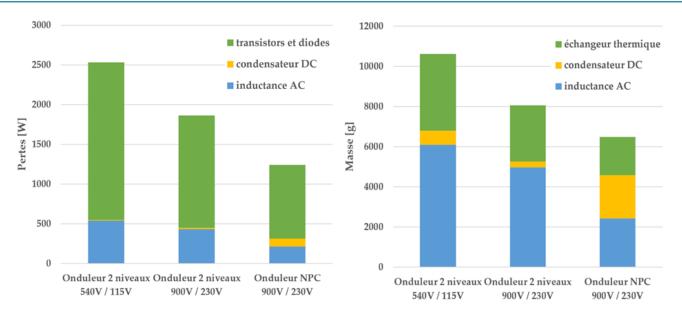

La comparaison de trois cas d'étude est disponible sur la figure 13. La répartition des pertes et de la masse pour le point de masse minimale de chaque front de Pareto apparaît sur la figure 14.

Figure 13 : Fronts de Pareto comparant les masses et rendements optimaux pour les deux onduleurs 2 niveaux et l'onduleur NPC

Figure 14 : Répartition des pertes et de la masse pour les différentes solutions considérées

La première conclusion de l'étude réside dans l'avantage de la montée en tension pour des fortes puissances converties. Cela permet de réduire les pertes par conduction, proportionnelles au carré du courant, dans les interrupteurs et les inductances. La masse globale diminue de 25% et le rendement augmente d'un point.

De plus, il apparaît que le passage à une structure NPC soulage à la fois les contraintes sur les interrupteurs et sur les inductances. En effet, la diminution du contenu harmonique introduite par la structure NPC permet de diminuer la taille du filtre AC mais aussi de diminuer la fréquence de découpage du convertisseur, ce qui amène à une baisse des pertes par commutation dans les interrupteurs. En revanche, le dimensionnement des condensateurs DC devient un point clé du problème, car il doivent gérer la circulation de l'harmonique trois en plus des harmoniques haute fréquence.

La présentation des résultats sous forme de front de Pareto permet de proposer plusieurs arbitrages entre deux indicateurs clés de la conception. C'est ensuite au client ou au décideur de choisir les performances qu'il souhaite, tout en ayant conscience des éventuelles particularités technologiques connues du concepteur, et n'apparaissant pas dans l'étude comparative.

#### 6 - Conclusion

Cet article résume des considérations essentielles pour la conception des onduleurs de tension à 2 niveaux et NPC. D'une part, des formules analytiques simples sont présentées pour évaluer la pertinence du choix de calibre en courant des interrupteurs pour respecter les contraintes thermique et les contraintes de rendement. D'autre part, des modèles relatifs au dimensionnement des inductances côté AC et des condensateurs côté DC permettent de tenir les contraintes de qualité d'énergie avec des composants de taille raisonnable. Le choix de la fréquence de découpage résulte d'un compromis entre qualité d'énergie et pertes par commutation. L'intérêt de la structure NPC est ici mise en lumière sur une problématique industrielle actuelle. Le passage d'une structure à 2 niveaux à NPC permet des gains sensibles sur la masse et les pertes du convertisseur. L'utilisation des modèles analytiques permet de chiffrer ce gain en fonction du cas d'application. Les gains de la structure NPC ne sont pas systématiques : cette démarche de modélisation doit être reprise pour chaque cahier des charges pour en tirer des conclusions appropriées.

# 7 - Ouvrages pour approfondir

- Electronique de puissance, de la cellule de commutation aux applications industrielles. Cours et exercices, A. Cunière, G. Feld, M. Lavabre, éditions Casteilla, 544 p. 2012.

- Mise en œuvre des composants électroniques de puissance, traité EGEM (électroniquegénie électrique-microsystèmes) sous la direction de Robert Perret, 2003, 326 p., Éditions Hermès Lavoisier.

- Electronique de puissance, méthodologie et convertisseurs élémentaires, Philippe Barrade, Presses Polytechniques et Universitaires Romandes.

- B.K. Bose, **Power electronics and variable frequency drives**, IEEE press, New York, 1997, 640p. TK 7881 P68 1997.

- R. Bausière, G. Séguier, F. Labrique, Les convertisseurs de l'électronique de puissance volume 4 : La conversion continu-alternatif, Tech. & Doc. Lavoisier, Paris, 1998, 561 p.

- Encyclopédie « Les techniques de l'ingénieur », Conversion de l'énergie électrique, rubrique convertisseurs électriques et application, articles D3060 à D3178.

## Références:

- [1] T. Meynard et G. Gateau, « Convertisseur Multiniveaux », Rev. 3EI, nº 72, p. 4-10, avr. 2013.

- [2] J. Rodriguez, Jih-Sheng Lai, et Fang Zheng Peng, « Multilevel inverters: a survey of topologies, controls, and applications », *IEEE Trans. Ind. Electron.*, vol. 49, n° 4, p. 724-738, août 2002, doi: 10.1109/TIE.2002.801052.

- [3] A. Leredde, « Study and Design of Multilevel Converters for High Power Applications », PhD, Institut National Polytechnique de Toulouse INPT, 2011. Consulté le : 27 février 2020. [En ligne]. Disponible sur : https://tel.archives-ouvertes.fr/tel-00668376

- [4] C. Rizet, « Amélioration du rendement des alimentations sans interruption », PhD, Université de Grenoble, 2011. Consulté le: 7 janvier 2020. [En ligne]. Disponible sur : https://tel.archives-ouvertes.fr/tel-00651973

- [5] J.-L. Schanen, « Electronique de puissance: au coeur de la commutation », Habilitation à Diriger des Recherches, Institut National Polytechnique de Grenoble INPG, 2000. [En ligne]. Disponible sur: https://theses.hal.science/tel-00689917

- [6] Infineon, « Double Pulse Testing: The How, What and Why », 2020.

- [7] C. P. Steinmetz, « On the Law of Hysteresis », *Trans. Am. Inst. Electr. Eng.*, vol. IX, n° 1, p. 1-64, janv. 1892, doi: 10.1109/T-AIEE.1892.5570437.

- [8] Magnetics, « Magnetics Powder Core Catalog ». [En ligne]. Disponible sur : https://www.mag-inc.com/Media/Magnetics/File-Library/Product%20Literature/Powder%20Core%20Literature/2017-Magnetics-Powder-Core-Catalog.pdf

- [9] A. Levasseur, « Nouvelles formules, valables à toutes les fréquences, pour le calcul rapide de l'effet Kelvin », *J Phys Radium*, vol. 1, n° 3, p. 93-98, 1930, doi: 10.1051/jphysrad:019300010309300.

- [10] J. W. Kolar et S. D. Round, « Analytical calculation of the RMS current stress on the DC-link capacitor of voltage-PWM converter systems », *IEE Proc. Electr. Power Appl.*, vol. 153, n° 4, p. 535-543, juill. 2006, doi: 10.1049/jp-epa:20050458.

- [11] M. Marzouk, « Development of integrated chargers for plug-in hybrid vehicles », PhD, Université Grenoble Alpes, 2015. Consulté le : 5 mars 2020. [En ligne]. Disponible sur : https://tel.archives-ouvertes.fr/tel-01239349

- [12] European Commission, ACARE Flightpath 2050 Europe's Vision for Aviation. in Policy / European Commission. Luxembourg: Publ. Off. of the Europ. Union, 2011.

- [13] A. Voldoire, « Outil de développement et d'optimisation dédié aux onduleurs SiC de forte puissance », phdthesis, Université Grenoble Alpes [2020-....], 2020. doi: 10/document.

Ressource publiée sur Culture Sciences de l'Ingénieur : <a href="https://eduscol.education.fr/sti/si-ens-paris-saclay">https://eduscol.education.fr/sti/si-ens-paris-saclay</a>